【事例】テストハンドラの静電気・発塵対策に有効な「ESD対応ケーブルキャリア」とは?

2026/04/30

- Thomas Engineering

増田 将吾

半導体やディスプレイの製造現場において、今や「歩留まり」は単なる指標ではなく、企業の競争力そのものです。

日本国産の先端半導体において、量産試作の歩留まりが90%以上だったと報じられたことは記憶に新しいでしょう。

さて、読者の皆様は改めて「歩留まり」をコストの観点で考えたことはあるでしょうか。歩留まりとは、原材料に対する良品割合、つまり「コストそのもの」です。例えば、歩留まりが50%と100%を比較すると、良品を確保するためにかかるコストは2倍も変わります。この差こそが、利益率を分ける決定的な要因となります。

特に、高速可動が求められるテストハンドラ工程では、「目に見えない微細な粉塵」と「予期せぬ静電気(ESD)」が、長年エンジニアを悩ませ、歩留まりの大きな壁となってきました。

今回は、この二大課題を同時に解決する「ESD対応型Thompod(トムポッド)システム」の真価に迫ります。

目次

・歩留まりはコストに直結する重要指標

・現場で発生していた課題

・解決策:ESD対応Thompodシステム

・導入効果:歩留まり改善に貢献

・まとめ 歩留まり改善は複合対策が鍵

|

【お急ぎの方へ】ESD対策・低発塵に最適なケーブルソリューション資料はこちら 資料ダウンロードはこちら |

現場で発生していた課題

韓国の半導体メーカーにおけるLSIテスト工程(テストハンドラ)では、以下のような課題が発生していました。

・ケーブルドラッグチェーン由来の発塵

・ケーブル断線やエアチューブの劣化によるダウンタイム

・可動部で発生する静電気(ESD)

テストハンドラは、約0.01秒/個という高速処理が求められるため、わずかな停止でも生産性に大きな影響を与えます。

特に静電気は、チップの電気特性評価に悪影響を及ぼすため、対策が不可欠でした。

解決策:ESD対応Thompodシステム

これらの課題に対し、低発塵構造を持つThompodシステムの導入が検討されました。

しかし、装置構造上、アルミ部材との接触による摩擦帯電の発生が新たな懸念として浮上しました。

そこで開発されたのが、ESD(静電気対策)対応Thompodシステムです。

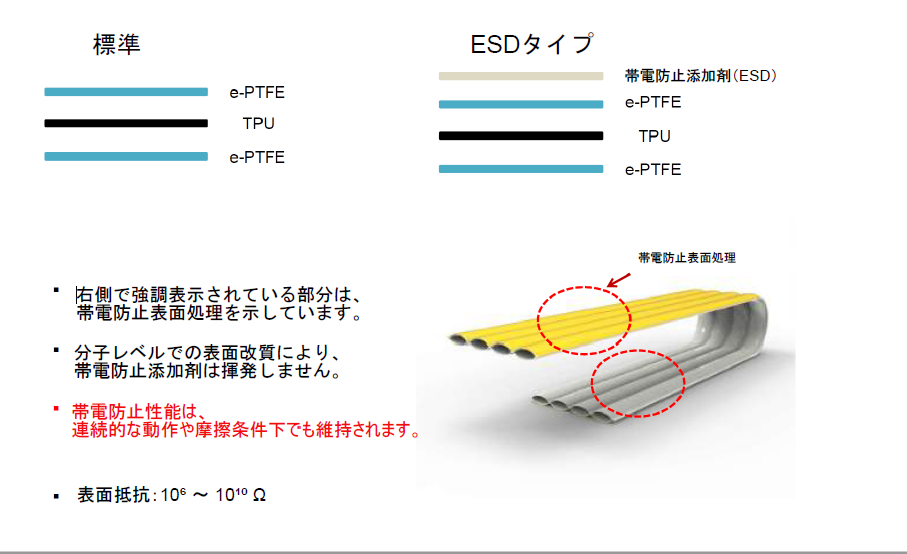

特長

・表面材質にe-PTFEを採用

・特殊コーティングにより摩擦帯電を低減

・低発塵構造によりクリーン環境に対応

図1:表面改質による帯電抑制構造

技術仕様・評価結果

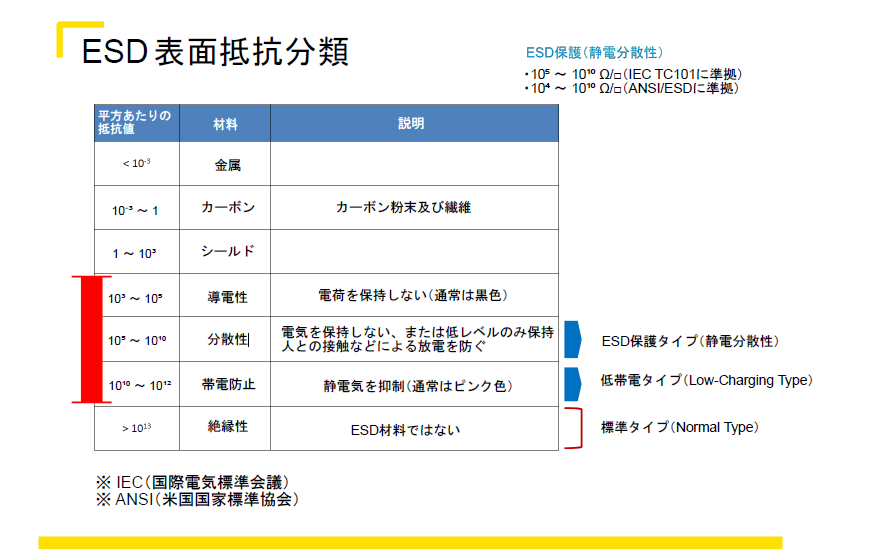

・表面抵抗値:10⁶〜10⁹ Ω(ESD散逸領域)

図2:ESD材料の表面抵抗値分類(IEC / ANSI規格に基づく)

・静電気電圧:規格内(±数Vレベル)

・耐摩耗試験:合格

・サイクル試験:合格

※ESD材料として、IECおよびANSI規格に準拠した評価を実施

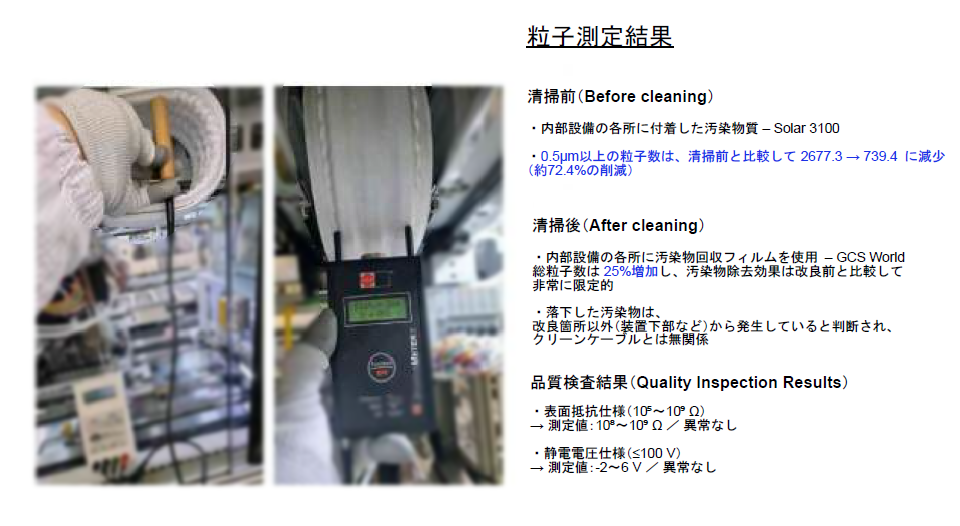

導入効果:歩留まり改善に貢献

本システムを導入した結果、以下のような改善が確認されました。

図3:パーティクル測定結果(導入前後比較)

・粉塵量:70%以上削減

・静電気特性:規格値内に安定

・ダウンタイムの低減

さらに、粒径0.5μm以上のパーティクル数においても大幅な減少が確認され、クリーン度の維持にも寄与しています。

まとめ|歩留まり改善は“複合対策”が鍵

今回の事例から分かるように、歩留まり改善には単一の対策ではなく、

・発塵対策

・静電気対策(ESD)

・可動部の信頼性向上

といった複合的なアプローチが重要です。

特に半導体・ディスプレイ製造装置においては、ケーブル周辺部品の見直しが、想像以上に大きな改善効果をもたらす可能性があります。

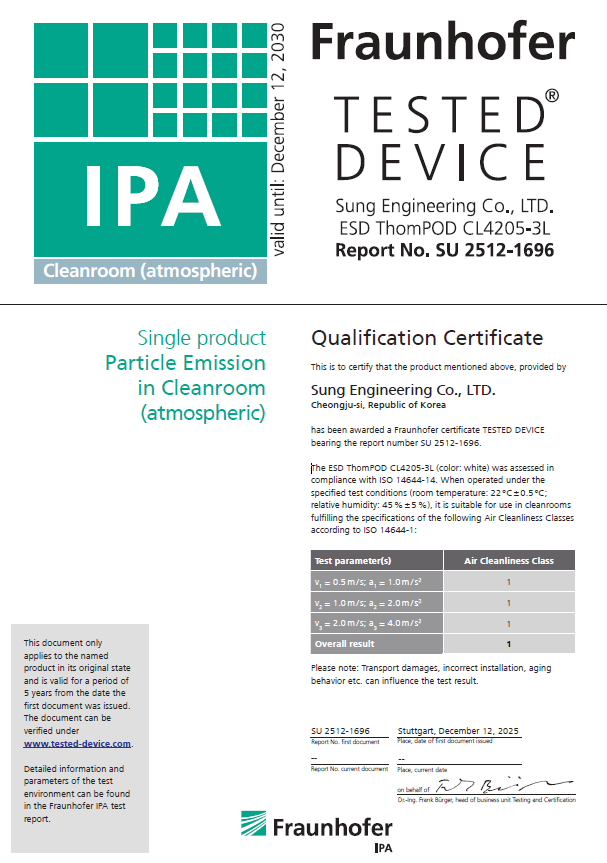

※Thompod社のケーブルドラッグチェーンはクリーンルーム規格IPAに合格しています。

次回は、さらに別の観点から歩留まり改善に寄与する技術についてご紹介予定です。

ぜひご期待ください。

本記事でご紹介したESD対策・低発塵技術について、より詳しい仕様や評価データは資料にまとめています。具体的な導入検討にご活用ください。

|

ESD対策・低発塵に最適なケーブルソリューション資料はこちら 資料ダウンロードはこちら |

増田 将吾プロダクトマネージャー

主にMurrplastikやBinderを担当しています。

ヨーロッパの優れた製品を幅広く皆様にご紹介していきたいです。

週末にはボルダリングジムに通って汗を流しています。

関連製品

関連カテゴリ

新着記事

-

2026/04/30

-

2026/04/30

-

2026/03/31

【Murrelektronik】次世代IO-Linkマスタ「pure.IO」が実現する工場DX ── IO-Linkのデイジーチェーン接続が可能に

-

2026/03/31

-

2026/03/30